干货 - 从软硬件层面,理解I2C总线是如何工作的!

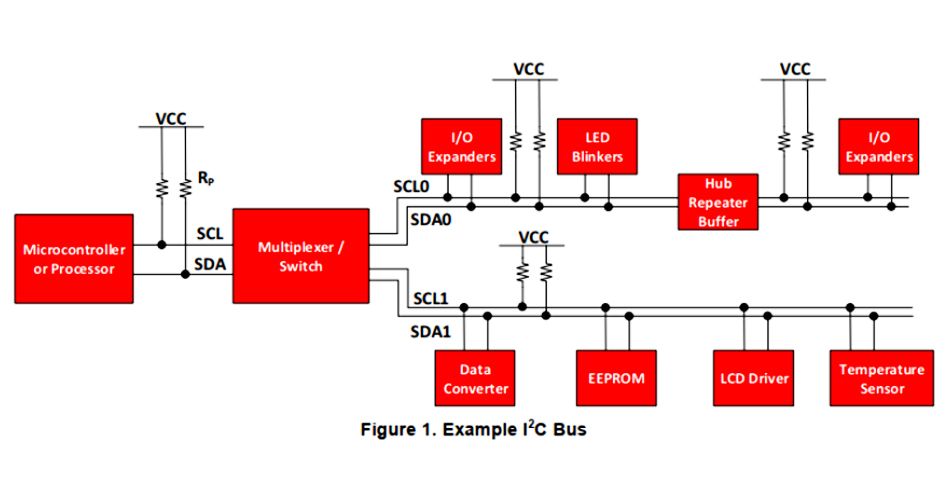

I2C总线是一种十分流行并且强大的总线,其多用于一个(或多个)主机与单个或多个从设备通讯的场景。图1表明了多种不同的外设可以共享这种只需要两根线便可以连接到处理器的总线,相对于其他接口来说,这也是I2C总线可以提供的最大优势之一。

这篇文章的目标是帮助电子工程师理解I2C总线是如何工作的。

图1展示了一个典型的用于嵌入式系统中的I2C总线,其上挂载了多种从设备。作为I2C主机的从微控制器控制着IO拓展、不同传感器、EEPROM、多个ADC/多个DAC、等等。所有这些设备只需要通过来自主机的两根引脚来控制。

图1

1、电特性

I2C总线使用开漏输出控制器,在同一线路上带有一个输入缓冲器,这样便可以允许在单根数据线上实现双向数据流传输。

1.1 用于双向通讯的开漏极

开漏输出极允许将总线上的电压拉低(大多数情况下是到地),或释放总线以允许其被上拉电阻拉高。当总线被主机或从机释放,线上的上拉电阻负责将线上电压上拉到电源轨。由于并没有设备可以在总线上输出高电平,这也就意味着总线在通讯中,将不会碰到一个设备输出高,而另一个设备试图输出低所导致的短路问题(电源轨到地)。I2C总线要求处于多主机环境下的单个主机在输出高而读回的实际总线电平为低时(这意味着另一个设备拉低了它)中止通讯,因为另一个设备正在使用总线。采用推挽输出方式的接口就没有这么自由了,这也正是I2C总线的一个优先。

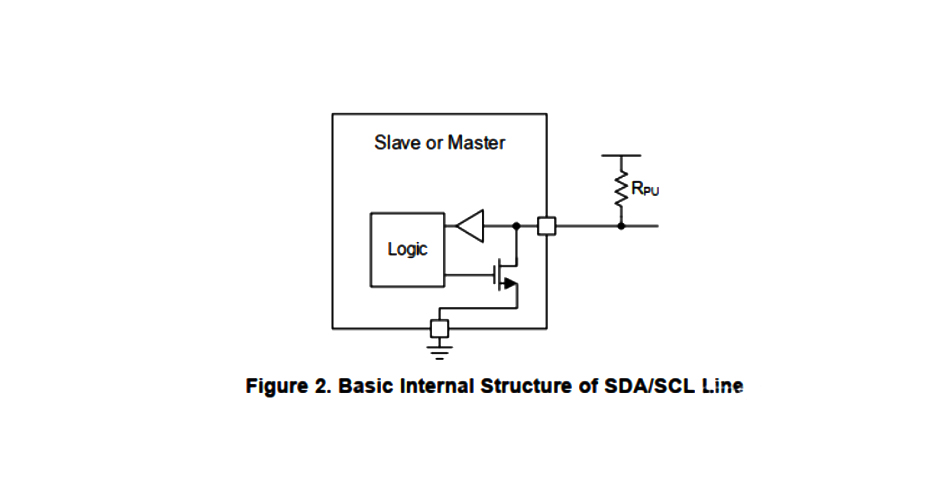

图2

图2展示了位于SDA/SCL线上的主从设备的内部简化结构,其由一个用于读取数据的缓冲器,以及一个用于发送数据的下拉场效应管组成。一个设备只被允许拉低总线(规定为短路到地)或释放总线(对地呈现高阻态)以允许上拉电阻拉升总线电平。当处理I2C设备时,有一个重要的概念需要阐明:没有设备可以保持总线为高。这个特性使得双向通讯得以实现。

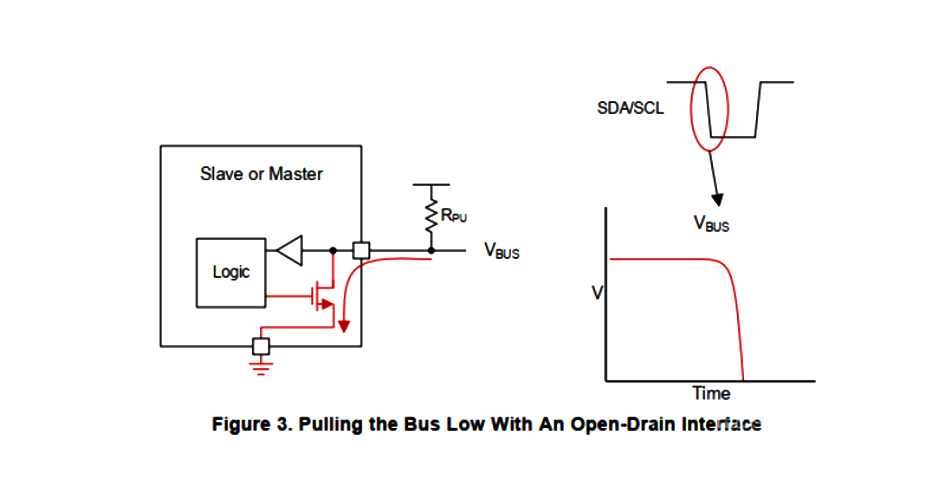

1.1.1 开漏极拉低

正如前面章节所述,开漏输出只能将总线拉低,或者释放总线然后依靠上拉电阻拉高总线。图3展示了总线拉低时的电流流向。当逻辑电路想要发送一个低电平时,其会使能下拉场效应管,场效应管会通过短路到地的方式拉低线路。

图3

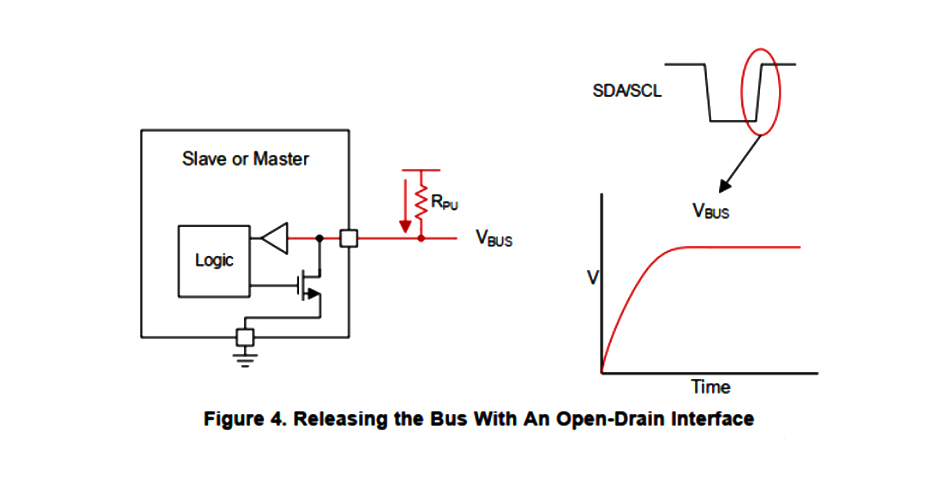

1.1.2 开漏极释放总线

当从机或主机想要传输一个逻辑电平高,它只能通过使能场效应管的方式释放总线。这将会使得总线处于浮空状态,同时上拉电阻将会将总线电平拉高到供电轨,此电平被当作高电平看待。图4展示了电流如何流过用于拉高总线的上拉电阻。

图4

2 I2C接口

2.1 I2C的常用操作

I2C总线是一种双向接口,其使用被称为主机的控制器与从设备进行通讯。从机不会主动传输任何数据,除非其被主机寻址。每个处于I2C总线上的设备均有独有的设备地址,以用于与位于同一总线上的其他设备做区分。很多从机需要在启动后进行配置以设置设备行为。这通常在主机访问从机的内部寄存器映射时完成,这些寄存器均有独一无二的寄存器地址。单个设备可以具有一个或多个寄存器,这些寄存器可以用来存储或读写数据。

I2C总线的物理接口由串行时钟线(SCL)和串行数据线(SDA)组成。SCL和SDA均需要通过上拉电阻连接到Vcc。上拉电阻的大小由I2C线路上的等效电容大小决定(想要了解更多,可以参考I2C Pull-up Resistor Calculation这份文档,文档号:SLVA689)。数据传送只能在总线空闲时初始化。如果SDA和SCL在一个STOP标志后均处于高电平状态,这时可以认为总线处在空闲状态。

主机访问从机的大体流程如下所示:

1、假设一个主机想要向从机发送数据:

发送方主机发送一个START标志并且寻址接收方从机

发送方主机发送数据到接收方从机

发送方主机通过发送STOP标志结束传输

2、如果主机想要从从机接收/读取数据:

接收方主机发送START标志并寻址发送方从机

接收方主机发送需要读取的寄存器地址到发送方从机

接收方主机从发送方从机接收数据

接收方主机通过发送STOP标志结束通讯

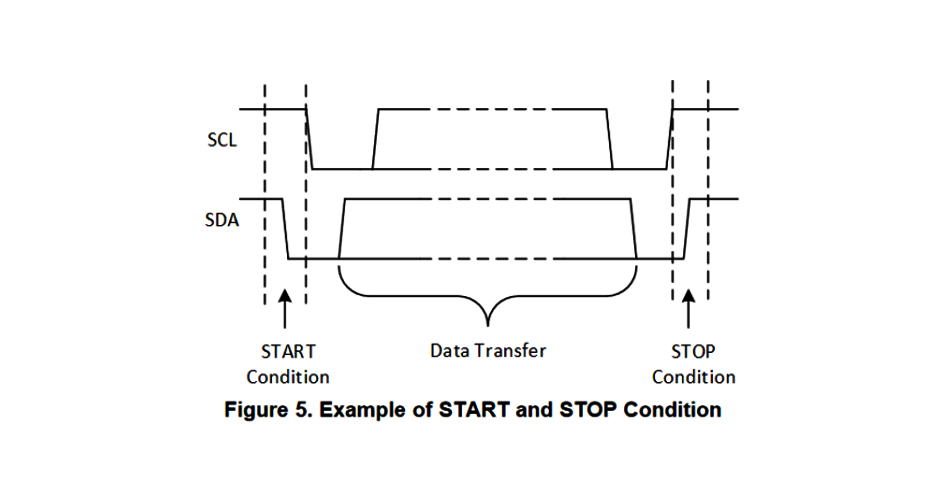

2.1.1 START与STOP标志

主机可以通过发送START标志初始化与设备的I2C通讯,或者发送STOP标志结束通讯。当SCL处于高电平时,SDA上的下降沿意味着一个START标志,而SDA上的上升沿意味着一个STOP标志。

图5

2.1.2 重复的START标志

重复的START标志与通常的START标志作用类似,其用于STOP标志后紧接START标志的情况时,用于代替这两者。它看上去与START标志一致,但是与START标志不同的是,重复的START标志在STOP标志之前出现(也就是总线不处于空闲状态时)。当主机希望开始一次新的通讯,但又不希望发送STOP标志使总线进入空闲状态时这会非常管用,这样可以防止当前主机的总线控制权被其他主机抢夺(当处于多主机环境下)。

2.2 数据有效性与字节格式

数据位伴随着SCL上的每一个时钟脉冲被传输。单个字节由SDA线上的8位数据组成,其可以是设备地址、寄存器地址或者读自/写入设备的数据。数据以大端在前(MSB)的方式传输。在START标志与STOP标志之间可以传输任意数量的数据字节。SDA线上的数据必须在时钟电平为高时保持稳定,因为SCL线为高时,SDA线上的变动将会被当作控制指令(START或STOP)。

图6

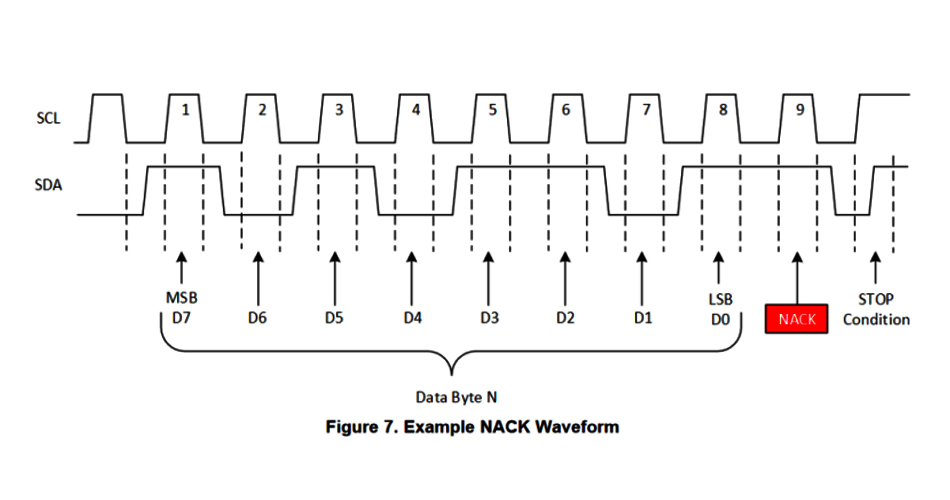

2.3 应答(ACK)和非应答(NACK)

数据的每一字节(包括地址字节)后总是伴随着来自接收方的1位ACK位。ACK位使得接收方可以告知发送方当前字节已成功接收,并且可以发送下一字节。

在接收方发送ACK位前,发送方必须释放总线。接收方通过在ACK/NACK时钟周期(第9时钟周期)的低电平相位拉低SDA线来发送一个ACK位,如此一来,SDA线将会在ACK/NACK时钟周期的高电平相位保持为低电平。设置与保持时间必须着重注意。

如果SDA线在ACK/NACK时钟周期保持为高电平,这将会被作为NACK。有好几种状态将会导致NACK的产生:

接收方无法进行接收或发送,因为其正在执行一些实时性功能(real-time function),无法与主机进行通讯。

在发送期间,接收方收到了无法识别的数据或指令。

在发送期间,接收方无法接收更多数据字节(也就是缓冲区满了)。

作为接收方的主机完成了数据读取,因此通过发送一个NACK通知从机。

图7

3、I2C总线数据

数据可以写入/读自从机,但是这是通过读写从设备内部的寄存器完成的。

包含信息的寄存器处于从机的内存中,无论这些信息是配置信息还是一些需要回发给主机的采样数据。为了指示从机去执行某一任务,主机必须向这些寄存器内写入信息。

虽然通常来说I2C从机是具有多个寄存器的,但也需要注意并不是所有从机都是这样。对于一个只具有单个寄存器的简易从机来说,可以通过在从机地址后直接发送数据的方式来直接写这个单一的寄存器,而不需要再对寄存器进行寻址。一个通过I2C总线控制的8位I2C开关可以很好的作为单寄存器设备的例子。由于它通过1位来使能/失能一个通道,因此只需要1个寄存器,主机可以在从机地址后直接写入寄存器数据,跳过寄存器编码部分。

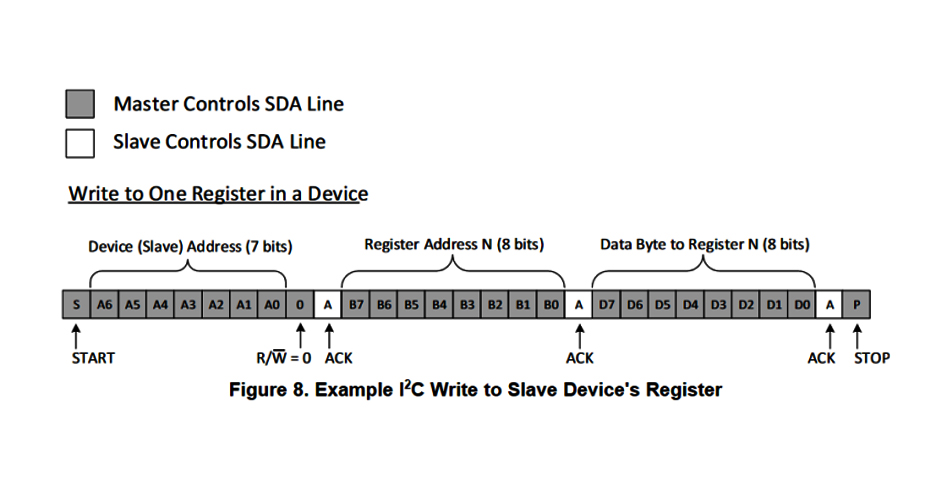

3.1 写位于I2C总线上的从机

要在I2C总线上执行写操作,主机会发送一个START标志以及从机地址到总线上,并且将最后1位(读写位)设为0以表明这是写操作。当从机发送应答位之后,主机便发送希望写入的寄存器地址。从机再一次应答,通知主机从机已准备好。这之后,主机开始发送寄存器数据到从机。当主机发送完所有需要发送的数据(有时只是一个字节),其将会通过发送STOP标志结束通讯。

图8展示了一个写入单个字节到从机寄存器的例子。

图8

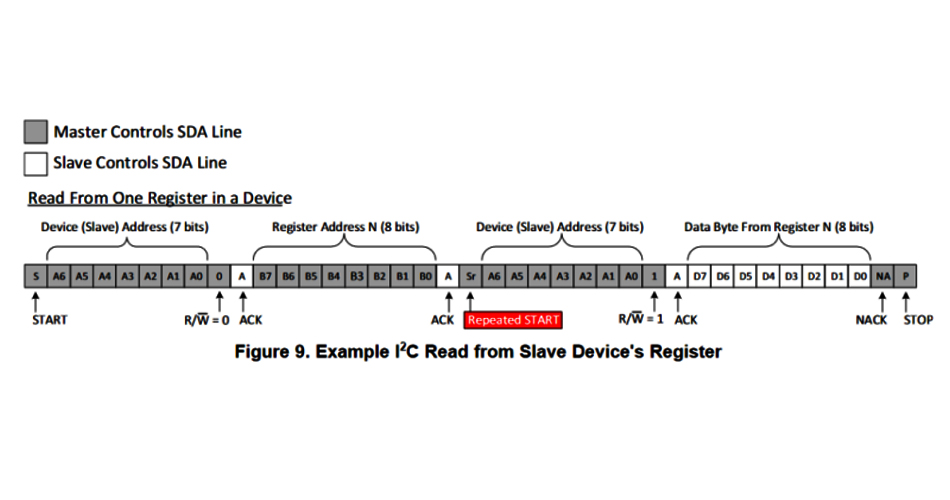

3.2 读位于I2C总线上的从机

从从机读取数据与写入数据类似,但是有一些额外的步骤。为了读取从机,主机必须先指示从机自己想要读取哪个寄存器。这一步通过执行与写操作类似的开始通讯步骤完成,发送读写位为0的设备地址(意味着一次写操作),紧跟着希望读的寄存器的地址。一旦从机应答了此地址,主机将会再一次发送START标志,并发送读写位为1的设备地址(意味着一次读操作)。这时,从机将会应答读请求,同时主机释放总线但是保持到从机的时钟供应。在通讯流程的这一部分,主机将会作为接收方主机,同时从机将会作为发送方从机。

主机将会继续发送时钟脉冲,但是会释放SDA线以便于从机传输数据。在每个字节数据的结尾,主机将会发送一个ACK到从机,让从机知道主机准备好接收更多的数据。一旦主机接收完成期待的字节数量,它将会发送一个NACK,通知从机终止通讯并要求从机释放总线。紧接着主机将会发送一个STOP标志结束通讯。

图9展示了从从机寄存器读取单个字节的例子。

图9